The most powerful and flexible architecture XGS-PON chipset in the market.

TREX1001

XGS-PON MAC Single Chip

Overview

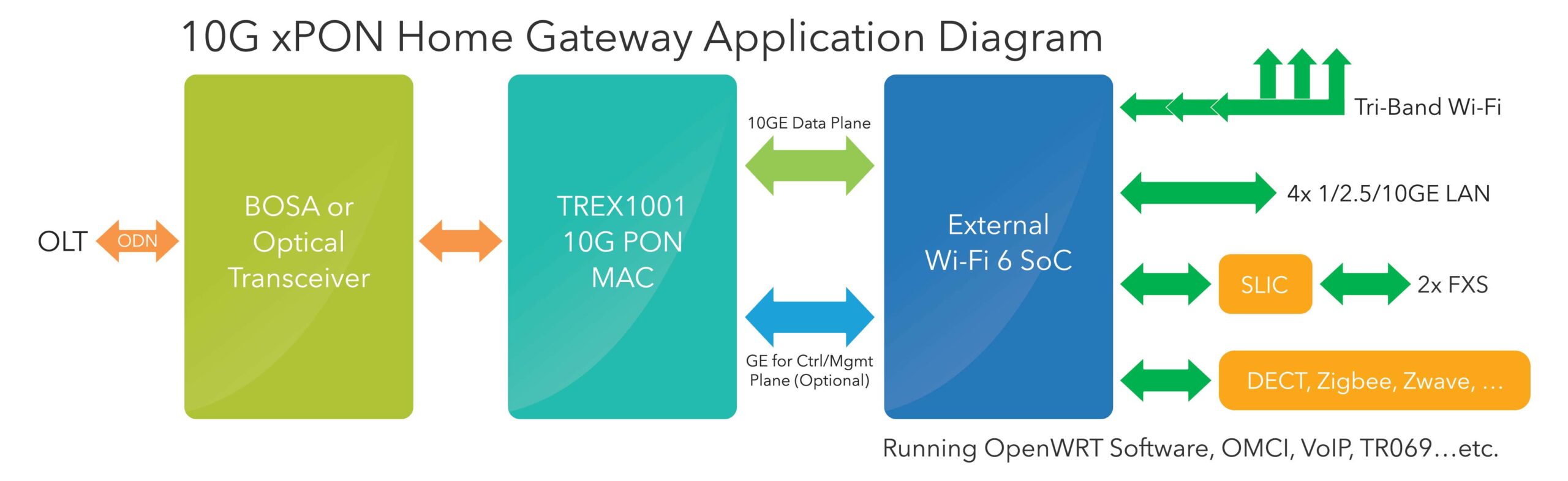

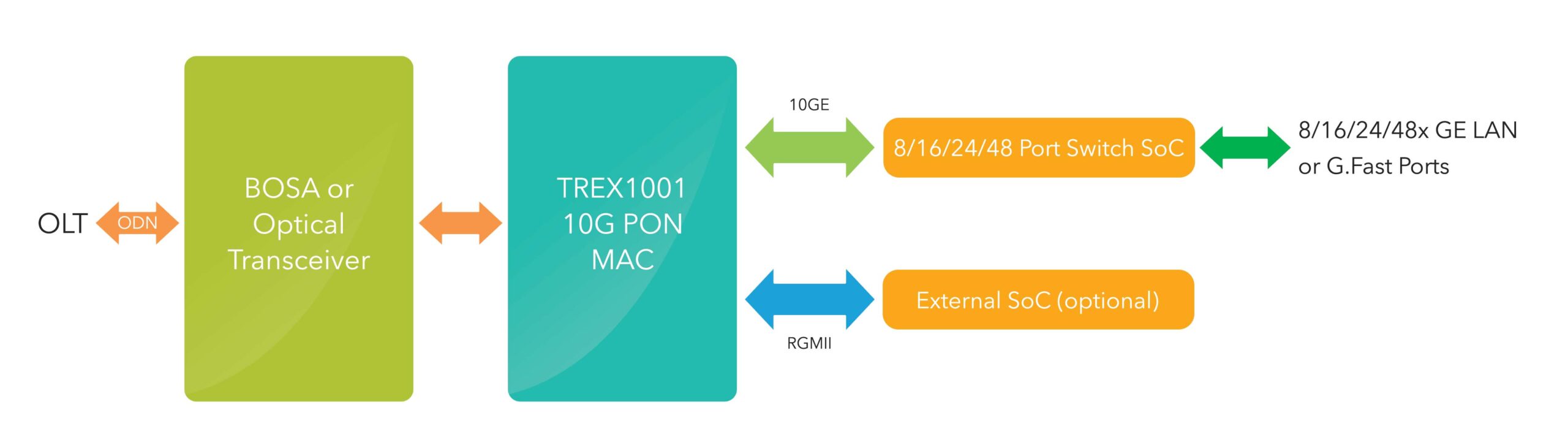

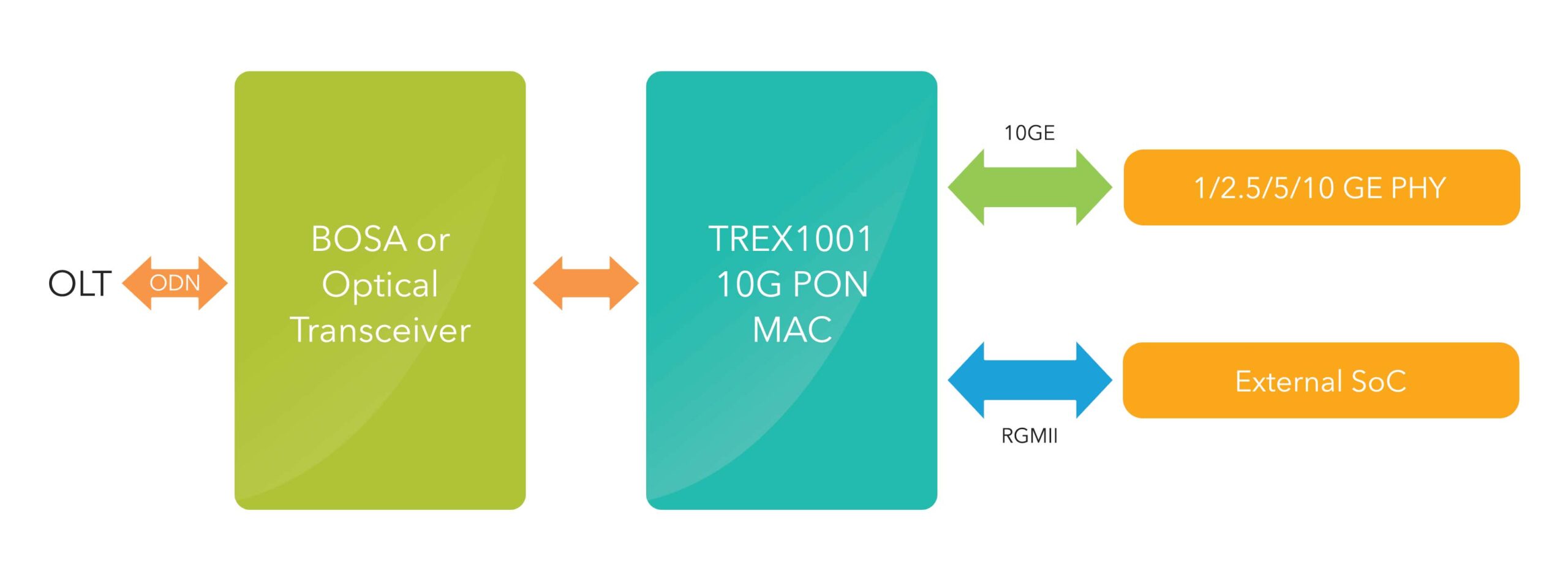

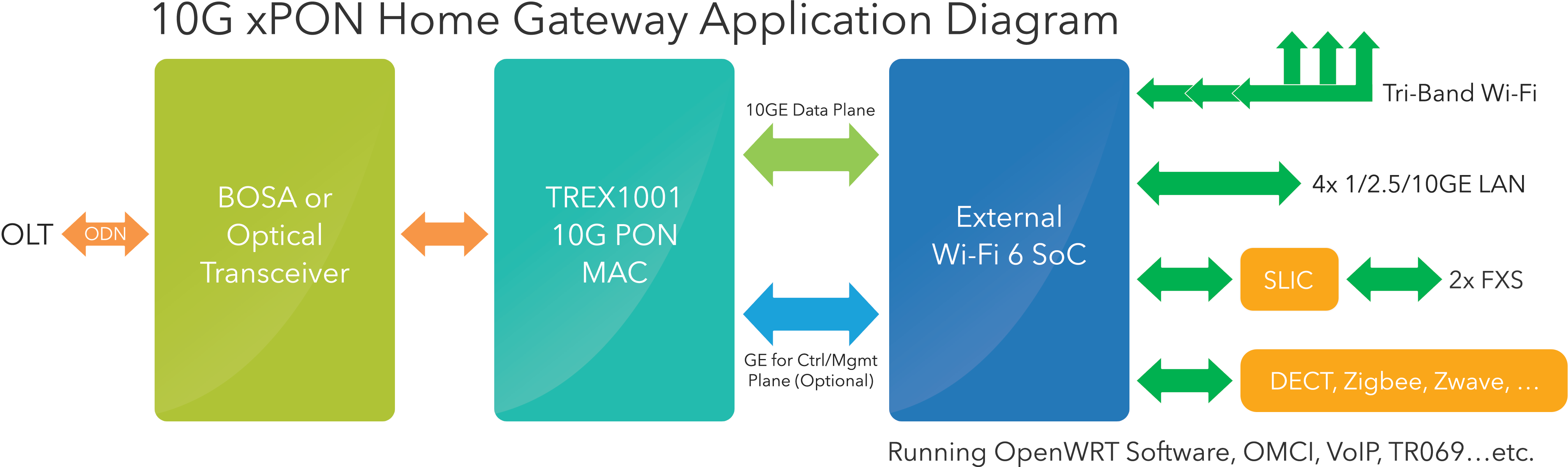

Block Diagram: Home Gateway | SFU | MDU

The TREX1001 is the world’s first CPU-less XGS-PON chipset that allows our technology partners to upgrade from older generation PON solutions to the newest XGS-PON protocol without having to re-engineer their software suite. The small footprint allows a broad range of product designs such as SFP+, SFU, home gateways, and fiber switches. The CPU-less design for home gateways can support 2×2 up to 4×4 802.11ax WiFi 6 tri-band solution. The flexibility allows various WiFi combinations that suits your specific applications.

Features

- PON MAC for ONU/ONT Compliant to ITU G.987.3 XGPON, G.9807.1 XGSPON, G.989.3 NGPON2

- Support line rate:

- DS: 9.95328Gbit/s, US: 2.48832Gbit/s for XGPON

- DS: 9.95328Gbit/s, US: 9.95328Gbit/s for XGSPON and NGPON2

- Support 32 TCONTs, 128 XGEMs, 128 PQs for U/S and 8 PQs for D/S with strict priority or WRR (weighted round robin)

- Support AES, key switching

- Support upstream and downstream FEC

- Support DBRu

- One PON SerDes interface to external optical tranceiver or BOSA on Board

- built-in PRBS generation and detection for SerDes for characterization and mass production

- Support Rogue ONU detection by monitoring TX_SD from the tranceiver module

- Support single-ended TX_BURST to turn on the laser driver

- Support line rate:

- Support Ethernet Adaption with

- VLAN tagging rule for 1024+8, with 128 protocol VLANs included

- Multicast Lookup Entries for 32+4

- 802.1p mapper

- Packet/Frame Trap based on L2/3/4 rules

- One LAN SerDes interface supports 1000BASE-X, 1/2.5G-SGMII 2.5G/5G- USGMII (Single-Port) or 10GBASE-R

- with built-in IEEE 802.3ae compliant MAC and PCS

- Support Flow Control and Pacing on LAN port

- One RGMII LAN interface

- In Band Management via 10GE LAN and Out-of-band management via RGMII interface

- Support 9k byte jumbo packets

- Support external reset input (from regulator or reset IC); or external RC reset with built-in reset circuitry

- Extenal 31.25MHz crystal with built-in oscillator circuitry for local reference clock

- Built-in low-jitter PLLs for the generation of clocks for system operation

- Built-in Dying Gasp Detection with Dying Gasp Output

- 8KHz and 2.048MHz Output for local synchronization

- Operating voltage: 0.9V for core, 1.8V for SerDes, 3.3V for I/Os

- Package: TFBGA, 7mmx7mm, 169 balls with ball-to-ball pitch 0.50mm